ModelSim是HDL仿真软件,Debussy是波形查看软件;搭配使用,相当爽

配置篇1 安装、和谐软件。略。

2 拷贝文件..\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll至文件夹..\modeltech_6.5\win32。

3 取消文件..\modeltech_6.5\modelsim.ini的只读属性后,打开。

找到

; Veriuser = veriuser.sl

替换为

Veriuser = novas.dll

保存;关闭;设为只读。

配置完,以后就一劳永逸了。

实战篇此处以一简单分频器为例。文件地图如下:

│ rtl.f

│ run.bat

│ sim.do

│

└─rtl

clk_rst.v

divider.v

divider_tb.v

1 编写欲仿真的HDL文件:RTL级代码+Testbench代码。保存在文件夹rtl中。

(1)divider.v // RTL级代码模块

`timescale 1ns/10ps

module divider(

input i_clk,

input i_rst_n,

output o_clk

);

parameter U_DLY = 1;

// log2(5) = 2.3219 <= 3

reg [2:0] cnt_p; // 上升沿计数子

// 5位上升沿计数器: 0 ~ 4

// 4 = 5 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_p <= 0;

else

begin

if (cnt_p == 4)

cnt_p <= 0;

else

cnt_p <= #U_DLY cnt_p + 1'b1;

end

end

// log2(5) = 2.3219 <= 3

reg [2:0] cnt_n; // 下降沿计数子

// 5位下降沿计数器: 0 ~ 4

// 4 = 5 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_n <= 0;

else

begin

if (cnt_n == 4)

cnt_n <= 0;

else

cnt_n <= #U_DLY cnt_n + 1'b1;

end

end

reg o_clk_p; // 上升沿时钟输出寄存器

// 输出上升沿时钟

// 0 ~ 2 ↑-> 1

// (2+1) ~ 4 ↑-> 0

// 2 = 5>>1

// 4 = 5 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_p <= 0;

else

begin

if (cnt_p <= 2) // 2 = 5>>1

o_clk_p <= 1;

else

o_clk_p <= 0;

end

end

reg o_clk_n; // 下降沿时钟输出寄存器

// 输出下降沿时钟

// 0 ~ 2 ↓-> 1

// (2+1) ~ 4 ↓-> 0

// 2 = 5>>1

// 4 = 5 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_n <= 0;

else

begin

if (cnt_n <= 2) // 2 = 5>>1

o_clk_n <= 1;

else

o_clk_n <= 0;

end

end

assign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码)

endmodule

(2)clk_rst.v // Testbench的时钟及复位模块

`timescale 1ns/10ps

module clk_rst(

output reg i_clk,

output reg i_rst_n

);

parameter CLK_PERIOD = 20;

parameter MULT_RATIO = 10;

parameter RESET_TIME = MULT_RATIO * CLK_PERIOD + 1;

initial

begin

i_rst_n <= 1'b0;

#RESET_TIME i_rst_n <= 1'b1;

end

initial

begin

i_clk <= 1'b0;

forever

#(CLK_PERIOD / 2) i_clk <= ~i_clk;

end

endmodule

把时钟及复位单独剥出来,便于移植到其他平台。

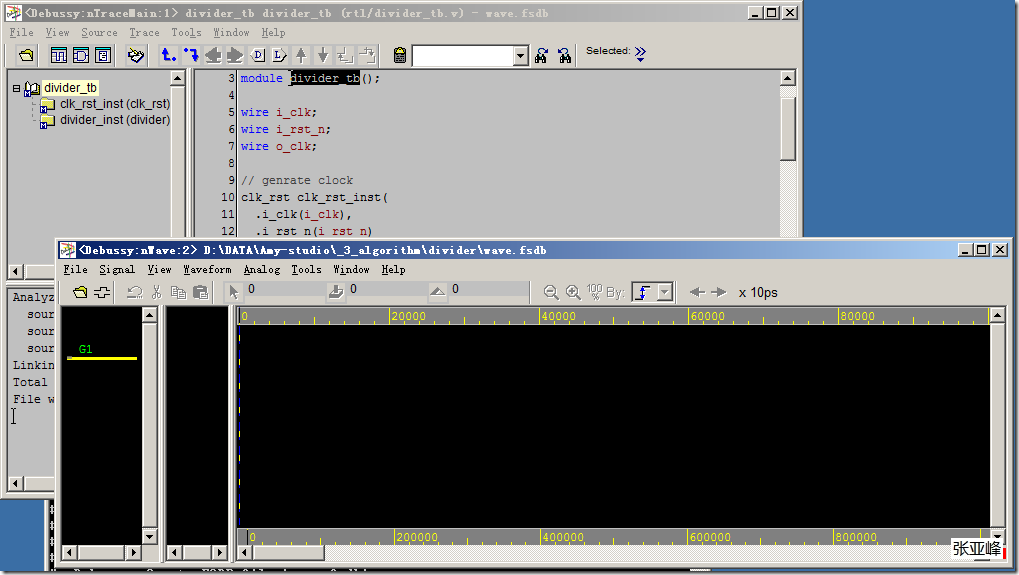

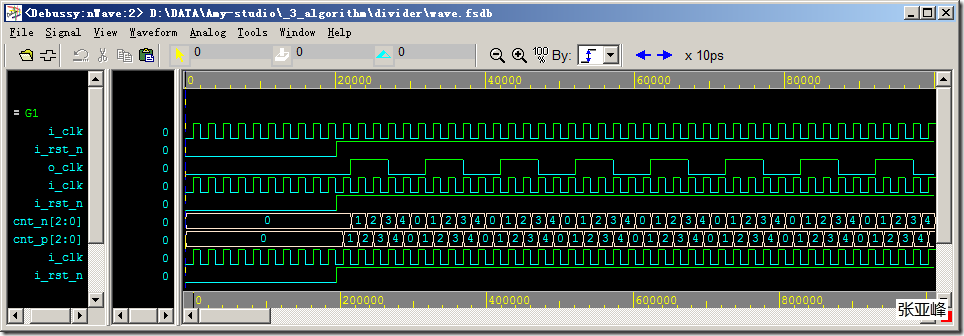

(3)divider_tb.v // Testbench顶层例化模块

`timescale 1ns/10ps

module divider_tb();

wire i_clk;

wire i_rst_n;

wire o_clk;

// genrate clock

clk_rst clk_rst_inst(

.i_clk(i_clk),

.i_rst_n(i_rst_n)

);

// user logic

divider divider_inst(

.i_clk(i_clk),

.i_rst_n(i_rst_n),

.o_clk(o_clk)

);

// dump fsdb file for debussy

initial

begin

$fsdbDumpfile("wave.fsdb");

$fsdbDumpvars;

end

endmodule

注意第22行到第27行

// dump fsdb file for debussy

initial

begin

$fsdbDumpfile("wave.fsdb");

$fsdbDumpvars;

end

这段语句的意思,就是调用ModelSim生成波形文件,并保存为wave.fsdb,供Debussy查看。

2 编写HDL文件列表文件,供ModelSim和Debussy使用。

rtl.f

rtl/divider.v rtl/clk_rst.v rtl/divider_tb.v

3 编写ModelSim命令行脚本文件。

sim.do

vlib work vlog -f rtl.f vsim work.divider_tb run 10us q

4 编写批处理脚步文件,调用命令行ModelSim生成波形文件,再调用Debusyy查看。

run.bat

::关闭回显 @ECHO OFF ::设置软件路径 SET debussy=C:\Novas\Debussy\bin\Debussy.exe SET vsim=C:\modeltech_6.5\win32\vsim.exe ::ModelSim Command %vsim% -c -do sim.do ::删除ModelSim生成的相关文件 RD work /s /q DEL transcript vsim.wlf /q ::Debussy Command %debussy% -f rtl.f -ssf wave.fsdb -2001 ::删除波形文件 DEL wave.fsdb /q ::删除Debussy生成的相关文件 RD Debussy.exeLog /s /q DEL debussy.rc /q ::退出命令行 EXIT

注意:请适当修改相关路径,本处仅以我个人的配置为例。

5 双击运行run.bat

显示命令行画面

ModelSim的功能太强大了,于是就有点繁琐。和Debussy协同仿真,我们就省却了许多不必要,何乐而不为呢

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。